臺積電公布技術路線圖,2025年量產N3X與N2工藝

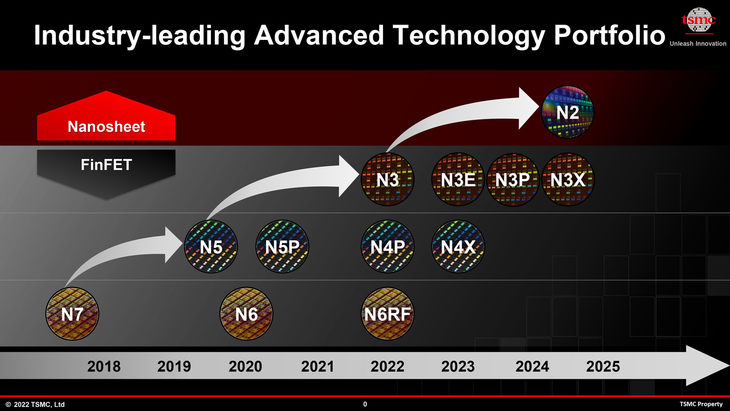

4月27日消息,臺積電在美國當地時間4月26日于美國加利福尼亞州圣克拉拉市舉辦了2023北美技術研討會。在此次臺積電舉辦的技術研討會上,臺積電官方進一步明確了旗下先進半導體制造工藝的路線圖,宣布將在2025年量產2nm工藝以及為高性能計算設備(HPC)而開發的N3X工藝。

臺積電官方表示,目前其規劃的3nm工藝家族有如下版本,分別是基礎的N3、成本優化的N3E、性能提升的N3P、為高性能計算設備使用的N3X、為車載設備準備的更為高壓耐受的N3 AE。

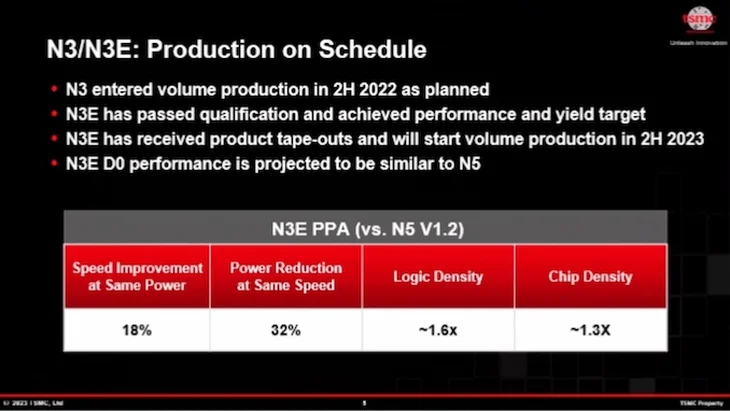

根據了解,臺積電旗下的N3E工藝相比較現階段的臺積電5nm工藝,可在相同頻率下降低 32% 的功耗,或者在相同功耗下提高 18% 的性能。而N3P則可在相同頻率下相比較于N3E降低5-10%的功耗,在同功耗的情況下提升5%的性能。

N3X則是優考慮HPC應用的性能和最大時鐘頻率。 因此其與N3P相比,N3X在驅動電壓為1.2V的情況下其速度提高了5% ,芯片密度與N3P相同。

N3AE則是面向汽車領域的工藝,其具備有更強的可靠性,臺積電表示將提供到相關的3nm開發SDK工具幫助開發廠商設計相關產品,并爭取在2025年帶來可在汽車上可靠使用的N3A工藝。

臺積電給出的時間表指出,其將在2023年推出基礎N3工藝以及N3E工藝的產品,2024年推出2024年推出N3P工藝相關產品,N3X和N3AE(N3A)將會在2025年進行推出。

臺積電官方也在次技術研討會上進一步向未接披露了2nm工藝計劃,其將在2nm工藝節點引入新型的 GAAFET 結構,即門全包圍場效應晶體管(Gate-All-Around FET)結構。臺積電官方表示,這種結構可以進一步提高晶體管密度和性能,并且降低功耗和泄漏。

臺積電介紹稱,相較于 N3E 制程技術,N2技術可在相同功耗下,性能最快增加 15%;在相同頻率下,功耗可降低 30%,同時晶片密度增加逾 15%。而這一N2工藝將會在2025年進入量產。

關注我們